# 2MHz, Super Chopper-Stabilized Operational Amplifier

The MC7650S Super Chopper-Stabilized Amplifier offers exceptionally low input offset voltage and is extremely stable with respect to time and temperature. It is a direct

replacement for the industry-standard MC7650 offering *improved* input offset voltage, *lower* input offset voltage temperature coefficient, *reduced* input bias current, and *wider* common mode voltage range. All improvements are highlighted in *bold italics* in the Electrical Characteristics section. *Critical parameters are guaranteed over the entire commercial temperature range.*

Intersil's unique CMOS chopper-stabilized amplifier circuitry is user-transparent, virtually eliminating the traditional chopper amplifier problems of intermodulation effects, chopping spikes, and overrange lockup.

The chopper amplifier achieves its low offset by comparing the inverting and non-inverting input voltages in a nulling amplifier, nulled by alternate clock phases. Two external capacitors are required to store the correcting potentials on the two amplifier nulling inputs; these are the only external components necessary

The clock oscillator and all the other control circuitry is entirely self-contained. However the 14 lead version includes a provision for the use of an external clock, if required for a particular application. In addition, the MC7650S is internally compensated for unity-gain operation.

# Features

- Guaranteed Max Input Offset Voltage for All Temperature Ranges

- Low Long-Term and Temperature Drifts of Input Offset Voltage

- Guaranteed Max Input Bias Current ......10pA

- Guaranteed Minimum Output Source/Sink Current

- Extremely High CMRR and PSRR.....140dB

- Unity-Gain Compensated

- Clamp Circuit to Avoid Overload Recovery Problems and Allow Comparator Use

- Extremely Low Chopping Spikes at Input and Output

- Improved, Direct Replacement for Industry-Standard MC7650 and other Second-Source Parts

- Pb-Free Plus Anneal Available (RoHS Compliant)

#### Ordering Information

| PART<br>NUMBER         | PART<br>MARKING | TEMP. RANGE (°C) | PACKAGE                   | PKG. DWG. # |

|------------------------|-----------------|------------------|---------------------------|-------------|

| ICL7650SCBA-1          | 7650S CBA-1     | 0 to +70         | 8 Ld SOIC                 | M8.15       |

| ICL7650SCBA-1T         | 7650S CBA-1     | 0 to +70         | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ICL7650SCBA-1Z (Note)  | 7650S CBA-1Z    | 0 to +70         | 8 Ld SOIC                 | M8.15       |

| ICL7650SCBA-1ZT (Note) | 7650S CBA-1Z    | 0 to +70         | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ICL7650SCPA-1          | 7650S CPA-1     | 0 to +70         | 8 Ld PDIP                 | E8.3        |

| ICL7650SCPA-1Z (Note)  | 7650S CPA-1Z    | 0 to +70         | 8 Ld PDIP* (Pb-free)      | E8.3        |

| ICL7650SCPD            | ICL7650SCPD     | 0 to +70         | 14 Ld PDIP                | E14.3       |

| ICL7650SCPDZ           | 7650SCPDZ       | 0 to +70         | 14 Ld PDIP* (Pb-free)     | E14.3       |

\*Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin

plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are

MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

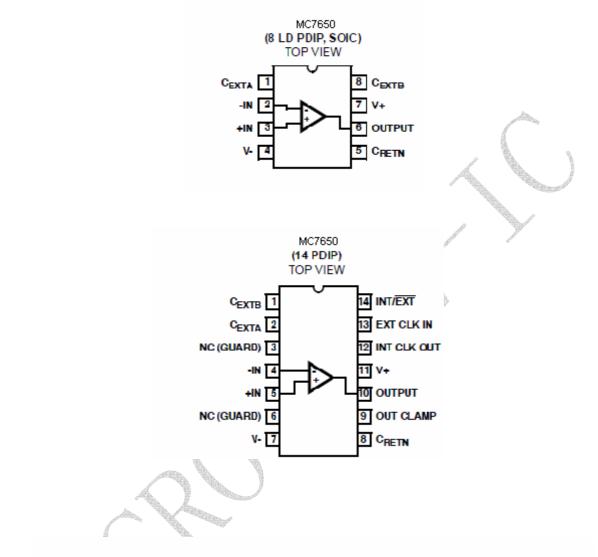

# **Pinouts**

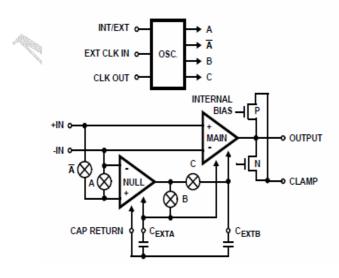

# **Functional Diagram**

Version 1.0

W

## Absolute Maximum Ratings Thermal Information

| Supply Voltage (V+ to V-)                                       |

|-----------------------------------------------------------------|

| Input Voltage                                                   |

| Voltage on Oscillator Control Pins                              |

| of Output Short Circuit Indefinite                              |

| Current to Any Pin                                              |

| While Operating (Note 1)                                        |

| Operating Conditions                                            |

| Temperature Range                                               |

| MC7650SC0°C to +70°C                                            |

| Thermal Information                                             |

| Thermal Resistance (Typical, Note 2) JA (°C/W) JC (°C/W)        |

| 8 Lead PDIP Package*                                            |

| 14 Lead PDIP Package                                            |

| 8 Lead SOIC Package                                             |

| Maximum Junction Temperature (Plastic Package) +150°C           |

| Maximum Storage Temperature Range55°C to +150°C                 |

| Pb-free reflow profile                                          |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp                |

| *Pb-free PDIPs can be used for through hole wave solder         |

| processing only. They are not intended for use in Reflow solder |

| processing applications                                         |

|                                                                 |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. NOTES:

1. Limiting input current to 100 µ A is recommended to avoid latchup problems. Typically 1mA is safe, however this is not guaranteed.

2. JA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications V<sub>SUPPLY</sub> = ±5V. See Test Circuit, Unless Otherwise Specified

| PARAMETER                                                           | SYMBOL                     | TEST CONDITIONS                          | TEMP.<br>(°C) | MIN  | түр              | МАХ | UNITS             |

|---------------------------------------------------------------------|----------------------------|------------------------------------------|---------------|------|------------------|-----|-------------------|

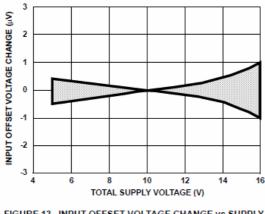

| Input Offset Voltage (Note 3)                                       | Vos                        |                                          | +25           | -    | ±0.7             | ±5  | μV                |

|                                                                     |                            |                                          | 0 to +70      | -    | ±1               | ±8  | μV                |

| Average Temperature Coefficient of<br>Input Offset Voltage (Note 3) | $\Delta V_{OS} / \Delta T$ |                                          | 0 to +70      | -    | 0.02             | -   | μV/°C             |

| Change in Input Offset with Time                                    | ΔV <sub>OS</sub> /ΔT       |                                          | +25           | -    | 100              | -   | nV/√month         |

| Input Bias Current   (+) ,  l(-)                                    | IBIAS                      |                                          | +25           | -    | 4                | 10  | pА                |

|                                                                     |                            |                                          | 0 to +70      | -    | 5                | 20  | pА                |

| Input Offset Current   (-),   (+)                                   | los                        |                                          | +25           | -    | 8                | 20  | pА                |

|                                                                     |                            |                                          | 0 to +70      | -    | 10               | 40  | pА                |

| Input Resistance                                                    | R <sub>IN</sub>            |                                          | +25           | -    | 10 <sup>12</sup> | -   | Ω                 |

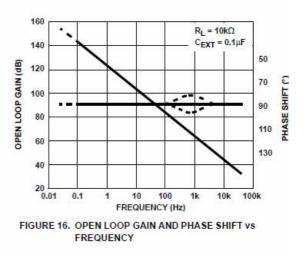

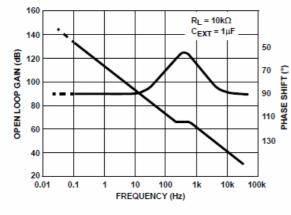

| Large Signal Voltage Gain (Note 3)                                  | AVOL                       | $R_L = 10k\Omega$ , $V_O = \pm 4V$       | +25           | 135  | 150              | -   | dB                |

|                                                                     |                            |                                          | 0 to +70      | 130  | -                | -   | dB                |

| Output Voltage Swing (Note 4)                                       | VOUT                       | R <sub>L</sub> = 10kΩ                    | +25           | ±4.7 | ±4.85            | -   | V                 |

|                                                                     |                            | R <sub>L</sub> = 100kΩ                   | +25           | -    | ±4.95            | -   | V                 |

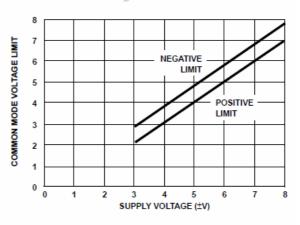

| Common Mode Voltage Range (Note 3)                                  | CMVR                       |                                          | +25           | -5   | -5.2 to +4       | 3.5 | V                 |

|                                                                     |                            |                                          | 0 to +70      | -5   | -                | 3.5 | V                 |

| Common Mode Rejection Ratio                                         | CMRR                       | CMVR = -5V to +3.5V                      | +25           | 120  | 140              | -   | dB                |

| (Note 3)                                                            |                            |                                          | 0 to +70      | 120  | -                | -   | dB                |

| Power Supply Rejection Ratio                                        | PSRR                       | $V_{S} = \pm 3V$ to $\pm 8V$             | +25           | 120  | 140              | -   | dB                |

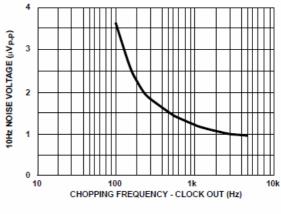

| Input Noise Voltage                                                 | e <sub>N</sub>             | R <sub>S</sub> = 100Ω,<br>f = DC to 10Hz | +25           | -    | 2                | -   | μV <sub>P-P</sub> |

| Input Noise Current                                                 | i <sub>N</sub>             | f = 10Hz                                 | +25           | -    | 0.01             | -   | pA/√Hz            |

| Gain Bandwidth Product                                              | GBWP                       |                                          | +25           | -    | 2                | -   | MHz               |

| Slew Rate                                                           | SR                         | $C_L = 50 pF, R_L = 10 k\Omega$          | +25           | -    | 2.5              | -   | V/µs              |

| Rise Time                                                           | t <sub>R</sub>             |                                          | +25           | -    | 0.2              | -   | μS                |

| Overshoot                                                           | OS                         |                                          | +25           | -    | 20               | -   | %                 |

| Operating Supply Range                                              | V+ to V-                   |                                          | +25           | 4.5  | -                | 16  | V                 |

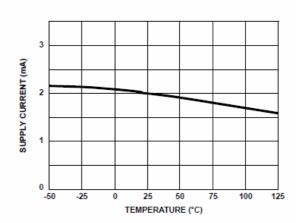

| Supply Current                                                      | I <sub>SUPP</sub>          | No Load                                  | +25           | -    | 2                | 3   | mA                |

|                                                                     |                            |                                          | 0 to +70      | -    | -                | 3.2 | mA                |

Version 1.0

#### Electrical Specifications V<sub>SUPPLY</sub> = ±5V. See Test Circuit, Unless Otherwise Specified (Continued)

| PARAMETER                   | SYMBOL    | TEST CONDITIONS           | TEMP.<br>(°C) | MIN | ТҮР   | МАХ | UNITS |

|-----------------------------|-----------|---------------------------|---------------|-----|-------|-----|-------|

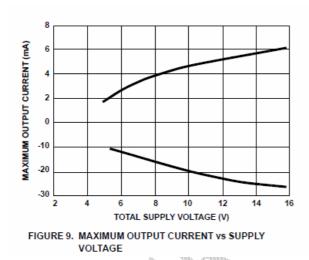

| Output Source Current       | IO SOURCE |                           | +25           | 2.9 | 4.5   | -   | mA    |

|                             |           |                           | 0 to +70      | 2.3 | -     | -   | mA    |

| Output Sink Current         | IO SINK   |                           | +25           | 25  | 30    | -   | mA    |

|                             |           |                           | 0 to +70      | 20  | -     | -   | mA    |

| Internal Chopping Frequency | fсн       | Pins 13 and 14 Open       | +25           | 120 | 250   | 375 | Hz    |

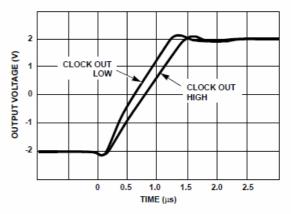

| Clamp ON Current (Note 5)   |           | R <sub>L</sub> = 100kΩ    | +25           | 25  | 70    | -   | μA    |

| Clamp OFF Current (Note 5)  |           | $-4V \le V_{OUT} \le +4V$ | +25           | -   | 0.001 | 5   | nA    |

|                             |           |                           | 0 to +70      | -   | -     | 10  | nA    |

#### NOTES:

3. These parameters are guaranteed by design and characterization, but not tested at temperature extremes because thermocouple effects prevent

precise measurement of these voltages in automatic test equipment.

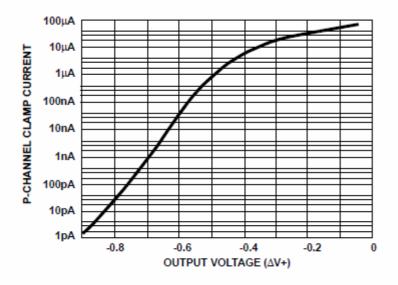

4. OUTPUT CLAMP not connected. See typical characteristic curves for output swing vs clamp current characteristics.

5. See OUTPUT CLAMP under detailed description.

6. All significant improvements over the industry-standard MC7650 are highlighted in bold italics.

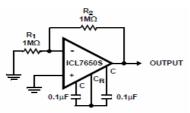

### Test Circuit

# **Application Information Detailed Description**

#### AMPLIFIER

The functional diagram shows the major elements of the MC7650S. There are two amplifiers, the main amplifier, and the nulling amplifier. Both have offset-null capability. The main amplifier is connected continuously from the input to the output, while the nulling amplifier, under the control of the chopping oscillator and clock circuit, alternately nulls itself and the main amplifier. The nulling connections, which are MOSFET gates, are inherently high impedance, and two external capacitors provide the required storage of the nulling potentials and the necessary nulling-loop time constants. The nulling arrangement operates over the full common-mode and power-supply

ranges, and is also independent of the output level, thus giving exceptionally high CMRR, PSRR, and AVOL. Careful balancing of the input switches, and the inherent balance of the input circuit, minimizes chopper frequency charge injection at the input terminals, and also the feed forward-type injection into the compensation capacitor, which is the main cause of output spikes in this type of circuit.

#### INTERMODULATION

Previous chopper-stabilized amplifiers have suffered from intermodulation effects between the chopper frequency and input signals. These arise because the finite AC gain of the amplifier necessitates a small AC signal at the input. This is seen by the zeroing circuit as an error signal, which is chopped and fed back, thus injecting sum and difference frequencies and causing disturbances to the gain and phase vs frequency characteristics near the chopping frequency. These effects are substantially reduced in the MC7650S by feeding the nulling circuit with a dynamic current, corresponding to the compensation capacitor current, in such a way as to cancel that portion of the input signal due to finite AC gain. Since that is the major error contribution to the MC7650S, the intermodulation and gain/phase disturbances are held to very low values, and can generally be ignored.

#### **CAPACITOR CONNECTION**

The null/storage capacitors should be connected to the CEXTA and CEXTB pins, with a common connection to the CRETN pin. This connection should be made directly by either a separate wire or PC trace to avoid injecting load current IR drops into the capacitive circuitry. The outside foil, where available, should be connected to CRETN. **OUTPUT CLAMP**

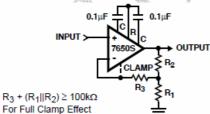

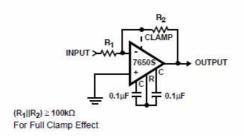

The OUTPUT CLAMP pin allows reduction of the overload recovery time inherent with chopper-stabilized amplifiers. When tied to the inverting input pin, or summing junction, a current path between this point and the OUTPUT pin occurs just before the device output saturates. Thus uncontrolled input differentials are avoided, together with the consequent charge buildup on the correction-storage capacitors. The output swing is slightly reduced.

#### Version 1.0

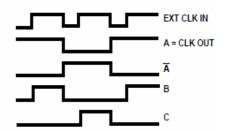

### CLOCK

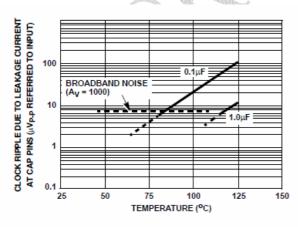

The MC7650S has an internal oscillator, giving a chopping frequency of 200Hz, available at the CLOCK OUT pin on the 14 pin devices. Provision has also been made for the use of an external clock in these parts. The INT/EXT pin has an internal pull-up and may be left open for normal operation, but to utilize an external clock this pin must be tied to V-to disable the internal clock. The external clock signal may then be applied to the EXT CLOCK IN pin. An internal divide-by-two provides the desired 50% input switching duty cycle. Since the capacitors

are charged only when EXT CLOCK IN is high, a 50% to 80% positive duty cycle is recommended, especially for higher frequencies. The external clock can swing between V+ and V-. The logic threshold will be at about 2.5V below V+. Note also that a signal of about 400 Hz, with a 70% duty cycle, will be

present at the EXT CLOCK IN pin with INT/EXT high or open. This is the internal clock signal before being fed to the divider. In those applications where a strobe signal is available, an alternate approach to avoid capacitor misbalancing during overload can be used. If a strobe signal is connected to EXT

CLK IN so that it is low during the time that the overload signal is applied to the amplifier, neither capacitor will be charged. Since the leakage at the capacitor pins is quite low at room temperature, the typical amplifier will drift less than  $10 \mu$  V/s, and relatively long measurements can be made with little change in offset.

## **COMPONENT SELECTION**

The two required capacitors, CEXTA and CEXTB, have optimum values depending on the clock or chopping frequency. For the preset internal clock, the correct value is  $0.1 \,\mu$  F, and to maintain the same relationship between the chopping frequency and the nulling time constant this value should be scaled approximately in proportion if an external clock is used. A high quality film type capacitor such as mylar is preferred, although a ceramic or other lower-grade capacitor may prove suitable in many applications. For quickest settling on initial turn-on, low dielectric absorption capacitors (such as polypropylene) should be used. With ceramic capacitors, several seconds may be required to settle to  $1 \,\mu$  V.

#### STATIC PROTECTION

All device pins are static-protected by the use of input diodes. However, strong static fields and discharges should be avoided, as they can cause degraded diode junction characteristics, which may result in increased input-leakage currents.

#### LATCHUP AVOIDANCE

Junction-isolated CMOS circuits inherently include a parasitic 4-layer (PNPN) structure which has characteristics similar to an SCR. Under certain circumstances this junction may be triggered into a low-impedance state, resulting in excessive supply current. To avoid this condition, no voltage greater than 0.3V beyond the supply rails should be applied to any pin. In general, the amplifier supplies must be established either at the same time or before any input signals are applied. If this is not possible, the drive circuits must limit input current flow to under 1mA to avoid latchup, even under fault conditions.

#### **OUTPUT STAGE/LOAD DRIVING**

The output circuit is a high-impedance type (approximately 18k ), and therefore with loads less than this value, the chopper amplifier behaves in some ways like a transconductance amplifier whose open-loop gain is proportional to load resistance. For example, the open-loop gain will be 17dB lower with a 1k load than with a 10k

proportional to load resistance. For example, the open-loop gain will be 17dB lower with a 1k load than with a 10k load. If the amplifier is used strictly for DC, this lower gain is of little consequence, since the DC gain is typically greater than 120dB even with a 1k load. However, for wideband applications, the best frequency response will be achieved with a load resistor of 10k or higher. This will result in a smooth 6dB/octave response from 0.1Hz to 2MHz, with phase shifts of less than 10° in the transition region where the main amplifier takes over from the null amplifier.

#### THERMO-ELECTRIC EFFECTS

The ultimate limitations to ultra-high precision DC amplifiers are the thermo-electric or Peltier effects arising in thermocouple junctions of dissimilar metals, alloys, silicon, etc. Unless all junctions are at the same temperature, thermoelectric voltages typically around  $0.1 \,\mu$  V/°C, but up to tens of mV/°C for some materials, will be generated. In order to realize the extremely low offset voltages that the chopper amplifier can provide, it is essential to take special precautions to avoid temperature gradients. All components should be enclosed to eliminate air

movement, especially that caused by power-dissipating elements in the system. Low thermoelectric-efficient connections should be used where possible and power supply voltages and power dissipation should be kept to a minimum. High-impedance loads are preferable, and good separation from surrounding heat-dissipating elements is advisable.

#### GUARDING

Extra care must be taken in the assembly of printed circuit boards to take full advantage of the low input currents of the MC7650S. Boards must be thoroughly cleaned with TCE or alcohol and blown dry with compressed air. After cleaning, the boards should be coated with epoxy or silicone rubber to prevent contamination.

Even with properly cleaned and coated boards, leakage currents may cause trouble, particularly since the input pins are adjacent to pins that are at supply potentials. This leakage can be significantly reduced by using guarding to lower the voltage difference between the inputs and adjacent metal runs. The guard, which is a conductive ring surrounding the inputs, is connected to a low impedance point that is at approximately the same voltage as the inputs. Leakage currents from high-voltage pins are then absorbed by the guard.

OUTPUT

FIGURE 1B. FOLLOWER

FIGURE 1A. INVERTING AMPLIFIER

INPL

$\begin{array}{l} \text{NOTE:} \ \ \begin{array}{c} R_1 R_2 \\ R_1^{+} R_2 \end{array} & \begin{array}{c} \text{SHOULD BE LOW} \\ \text{IMPEDANCE FOR} \\ \text{OPTIMUM GUARDING} \end{array} \\ \textbf{FIGURE 1C. NON-INVERTING AMPLIFIER} \end{array}$

FIGURE 1. CONNECTION OF INPUT GUARDS

#### **PIN COMPATIBILITY**

The basic pinout of the 8-pin device corresponds, where possible, to that of the industry standard 8-pin devices, the LM741, LM101, etc. The null-storing external capacitors are connected to pins 1 and 8, usually used for offset null or compensation capacitors, or simply not connected. In the case of the OP-05 and OP-07 devices, the replacement of the offset-null pot, connected between pins 1 and 8 and V+, by two capacitors from those pins to pin 5, will provide easy compatibility. As for the LM108, replacement of the compensation capacitor between pins 1 and 8 by the two capacitors to pin 5 is all that is necessary. The same operation, with the removal of any connection to pin 5, will suffice for the LM101,  $\mu$ A748, and similar parts.

The 14-pin device pinout corresponds most closely to that of the LM108 device, owing to the provision of "NC" pins for guarding between the input and all other pins. Since this device does not use any of the extra pins, and has no provision for offset-nulling, but requires a compensation capacitor, some changes will be required in layout to convert it to the MC7650S.

# **Typical Applications**

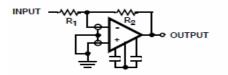

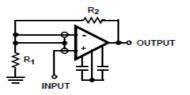

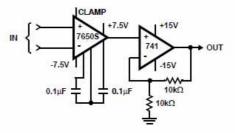

Clearly the applications of the MC7650S will mirror those of other op amps. Anywhere that the performance of a circuit can be significantly improved by a reduction of input-offset voltage and bias current, the MC7650S is the logical choice. Basic non-inverting and inverting amplifier circuits are shown in Figures 2 and 3. Both circuits can use the output clamping circuit to enhance the overload recovery performance. The only limitations on the replacement of other op amps by the MC7650S are the supply voltage (±8V Max) and the output drive capability (10k load for full swing). Even these limitations can be overcome using a simple booster circuit, as shown in Figure 4, to enable the full output capabilities of the LM741 (or any other standard device) to be combined with the input capabilities of the MC7650S. The pair form a composite device, so loop gain stability, when the feedback network is added, should be watched carefully.

NOTE: R1||R2 indicates the parallel combination of R1 and R2.

FIGURE 2. NON INVERTING AMPLIFIER WITH OPTIONAL CLAMP

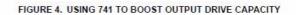

Figure 5 shows the use of the clamp circuit to advantage in a zero-offset comparator. The usual problems in using a chopper stabilized amplifier in this application are avoided, since the clamp circuit forces the inverting input to follow the input signal. The threshold input must tolerate the output clamp current VIN/R without disturbing other portions of the system

The pin configuration of the 14 pin dual in-line package is designed to facilitate guarding, since the pins adjacent to the inputs are not used (this is different from the standard 741 and 101A pin configuration, but corresponds to that of the LM108).

NOTE:  $R_1||R_2$  indicates the parallel combination of  $R_1$  and  $R_2$ . FIGURE 3. INVERTING AMPLIFIER WITH (OPTIONAL) CLAMP

FIGURE 5. LOW OFFSET COMPARATOR

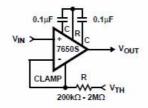

NOTE: For further Applications Assistance, see AN053. FIGURE 6. ICL8048 OFFSET NULLED BY MC7650S

Normal logarithmic amplifiers are limited in dynamic range in the voltage-input mode by their input-offset voltage. The built-in temperature compensation and convenience features of the ICL8048 can be extended to a voltage-input dynamic range of close to 6 decades by using the MC7650S to offset-null the ICL8048, as shown in Figure 6. The same concept can also be used with such devices as the HA2500 or HA2600 families of op amps to add very low offset voltage capability to their very high slew rates and bandwidths. Note that these circuits will also have their DC gains, CMRR, and PSRR enhanced.

### **Typical Performance Curves**

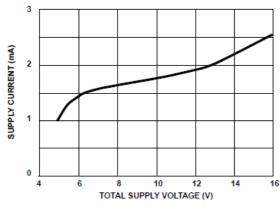

FIGURE 7. SUPPLY CURRENT vs SUPPLY VOLTAGE

FIGURE 8. SUPPLY CURRENT vs AMBIENT TEMPERATURE

FIGURE 10. COMMON MODE INPUT VOLTAGE RANGE vs SUPPLY VOLTAGE

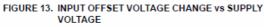

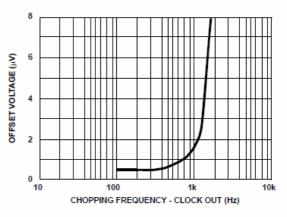

FIGURE 12. 10Hz NOISE VOLTAGE vs CHOPPING FREQUENCY

# Typical Performance Curves (Continued)

#### Typical Performance Curves (Continued)

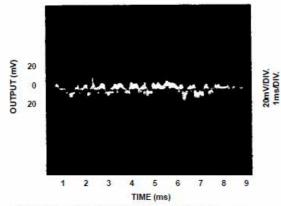

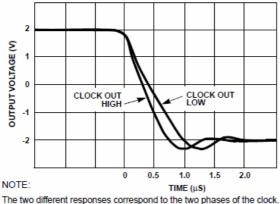

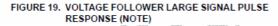

NOTE: The two different responses correspond to the two phases of the clock.

FIGURE 18. VOLTAGE FOLLOWER LARGE SIGNAL PULSE RESPONSE (NOTE)

FIGURE 20. N-CHANNEL CLAMP CURRENT vs OUTPUT VOLTAGE

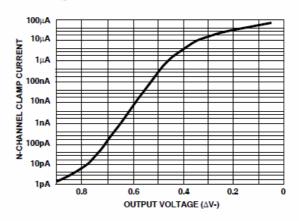

FIGURE 21. P-CHANNEL CLAMP CURRENT vs OUTPUT VOLTAGE

Version 1.0

# **4** MC7650

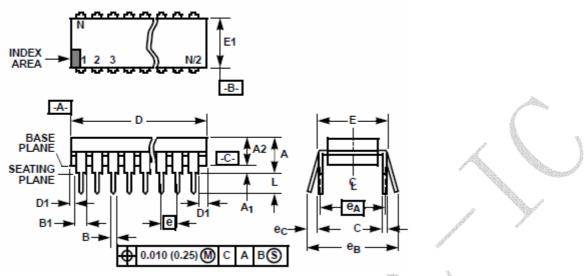

Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

1. Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

5. D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

${\bf 6.}~{\bf E}$  and are measured with the leads constrained to be perpendicular to datum .

7. eB and eC are measured at the lead tips with the leads unconstrained. eC must be zero or greater.

8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).9. N is the maximum number of terminal positions.

10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

#### E8.3 (JEDEC MS-001-BA ISSUE D) 8 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES N |           | MILLIM |       |       |

|----------------|----------|-----------|--------|-------|-------|

| SYMBOL         | MIN      | MAX       | MIN    | MAX   | NOTES |

| Α              | -        | 0.210     | -      | 5.33  | 4     |

| A1             | 0.015    | -         | 0.39   | -     | 4     |

| A2             | 0.115    | 0.195     | 2.93   | 4.95  | -     |

| В              | 0.014    | 0.022     | 0.356  | 0.558 | -     |

| B1             | 0.045    | 0.070     | 1.15   | 1.77  | 8, 10 |

| С              | 0.008    | 0.014     | 0.204  | 0.355 | -     |

| D              | 0.355    | 0.400     | 9.01   | 10.16 | 5     |

| D1             | 0.005    | -         | 0.13   | -     | 5     |

| E              | 0.300    | 0.325     | 7.62   | 8.25  | 6     |

| E1             | 0.240    | 0.280     | 6.10   | 7.11  | 5     |

| е              | 0.100    | 0.100 BSC |        | BSC   | -     |

| eA             | 0.300    | BSC       | 7.62   | BSC   | 6     |

| е <sub>В</sub> | -        | 0.430     | -      | 10.92 | 7     |

| L              | 0.115    | 0.150     | 2.93   | 3.81  | 4     |

| N              | 8        |           | 8      |       | 9     |

Rev. 0 12/93

# **4** MC7650

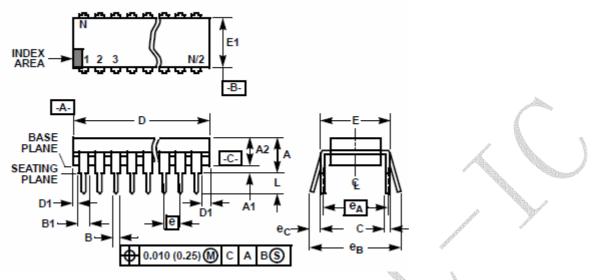

Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

1. Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

5. D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

6. E and are measured with the leads constrained to be perpendicular to datum .

7. eB and eC are measured at the lead tips with the leads unconstrained. eC must be zero or greater.

8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

9. N is the maximum number of terminal positions.

10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

#### E14.3 (JEDEC MS-001-AA ISSUE D) 14 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INC   | HES   | MILLIM   |       |             |

|----------------|-------|-------|----------|-------|-------------|

| SYMBOL         | MIN   | MAX   | MIN      | MAX   | NOTES       |

| Α              | -     | 0.210 | -        | 5.33  | 4           |

| A1             | 0.015 | -     | 0.39     | -     | 4           |

| A2             | 0.115 | 0.195 | 2.93     | 4.95  | -           |

| В              | 0.014 | 0.022 | 0.356    | 0.558 | -           |

| B1             | 0.045 | 0.070 | 1.15     | 1.77  | 8           |

| С              | 0.008 | 0.014 | 0.204    | 0.355 | -           |

| D              | 0.735 | 0.775 | 18.66    | 19.68 | 5           |

| D1             | 0.005 | -     | 0.13     | -     | 5           |

| E              | 0.300 | 0.325 | 7.62     | 8.25  | 6           |

| E1             | 0.240 | 0.280 | 6.10     | 7.11  | 5           |

| е              | 0.100 | BSC   | 2.54 BSC |       | -           |

| e <sub>A</sub> | 0.300 | BSC   | 7.62     | BSC   | 6           |

| е <sub>В</sub> | -     | 0.430 | -        | 10.92 | 7           |

| L              | 0.115 | 0.150 | 2.93     | 3.81  | 4           |

| N              | 1     | 4     | 1        | 4     | 9           |

|                |       |       |          | Re    | ev. 0 12/93 |

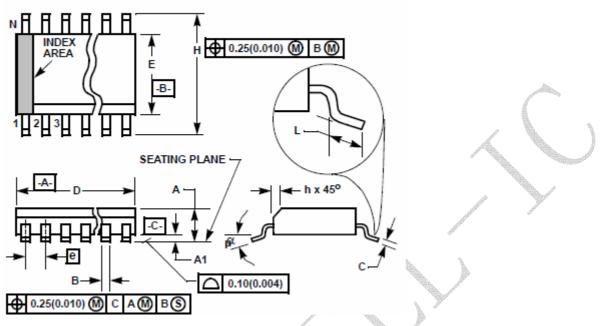

# Small Outline Plastic Packages (SOIC)

NOTES:

1. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension "D" does not include mold flash, protrusions or gate burrs.Mold flash, protrusion and gate burrs shall not exceed

0.15mm (0.006 inch) per side.

4. Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

6. "L" is the length of terminal for soldering to a substrate.

7. "N" is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

# M8.15 (JEDEC MS-012-AA ISSUE C)

| 8 LEAD NARROW BODY SMALL OU | UTLINE PLASTIC PACKAGE |

|-----------------------------|------------------------|

|-----------------------------|------------------------|

| 8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE |        |        |          |      |       |  |

|--------------------------------------------------|--------|--------|----------|------|-------|--|

|                                                  | INCHES |        | MILLIM   |      |       |  |

| SYMBOL                                           | MIN    | MAX    | MIN      | MAX  | NOTES |  |

| Α                                                | 0.0532 | 0.0688 | 1.35     | 1.75 | -     |  |

| A1                                               | 0.0040 | 0.0098 | 0.10     | 0.25 | -     |  |

| В                                                | 0.013  | 0.020  | 0.33     | 0.51 | 9     |  |

| С                                                | 0.0075 | 0.0098 | 0.19     | 0.25 | -     |  |

| D                                                | 0.1890 | 0.1968 | 4.80     | 5.00 | 3     |  |

| E                                                | 0.1497 | 0.1574 | 3.80     | 4.00 | 4     |  |

| е                                                | 0.050  | BSC    | 1.27 BSC |      | -     |  |

| н                                                | 0.2284 | 0.2440 | 5.80     | 6.20 | -     |  |

| h                                                | 0.0099 | 0.0196 | 0.25     | 0.50 | 5     |  |

| L                                                | 0.016  | 0.050  | 0.40     | 1.27 | 6     |  |

| N                                                | 8      |        | 1        | В    | 7     |  |

| α                                                | 0° 8°  |        | 0°       | 8°   | -     |  |

|                                                  |        |        |          |      |       |  |

Rev. 1 6/05